HDL Works IO Checker v2.2.R2 for Linux 英文正式版(電子設計軟體)

破解說明:

關掉主程式,破解檔放置於crack夾內,請將破解檔複製於主程式的安裝目錄內既可破解

內容說明:

驗證在幾分鐘內FPGA的IO引腳PCB和FPGA之間的數百- 當使用大型FPGA在PCB上的FPGA管腳連接

到正確的信號,是一項繁重的任務。 FPGA上的方引腳被分配到頂層的HDL信號在FPGA上實現的

邏輯。 PCB上側引腳連接到適當的網,將它連接到其他元件在PCB上。由於FPGA和PCB的實施往

往是做平行,所使用的信號名稱並不總是相同的。為了使事情更糟的是,它往往是必要的執行

針掉期防止PCB布線問題。這些引腳互換作出FPGA和PCB上。由於這是幾乎總是體力勞動,目前的

設備已超過1500針,容易犯一個錯誤。

英文說明:

Verifying hundreds of FPGA IO pins between PCB and FPGA in minutes

- When using large FPGA's on a PCB making sure that the FPGA pins are

connected to the right signals is a cumbersome task. On the FPGA side

the pins are assigned to the HDL signals that form the toplevel of the

logic implemented on the FPGA. On the PCB side the pins have to be

connected to the proper net that will connect it to other components

on the PCB. Because implementation of FPGA and PCB is often done in

parallel, the signal names used are not always identical. To make

things even worse, it is often necessary to perform pin swaps to

prevent PCB routing problems. These pin swaps have to be made both

on the FPGA and the PCB. As this is almost always manual work, and

current devices have over 1500 pins, a mistake is easily made.

Intelligent Verification

- IO Checker uses rules (based on regular expressions) to match the

signal names in both the FPGA and PCB design environment. It allows

the tool to validate groups of matches although individual signals can

still differ. The rules can be generated automatically and be fine-tuned

by the designer. The automated approach will often match 80% to 90% of

all device pins.

- The flexibility of IO Checker allows it to be used in any design flow

and does not require any design methodology. The rules generator in

combination with the sorted problem view allows

Engineers to validate

a 1000+ pins device in half an hour.

- Once the project and its rules are defined it is a simple task to keep

the FPGA and PCB data consistent. All out-of-date files are processed in

one action and all changes are reported.

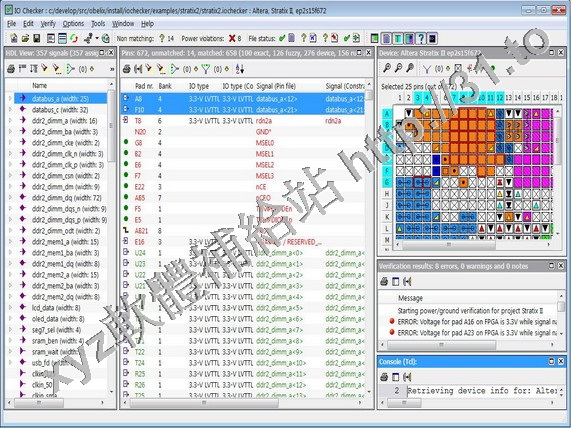

圖片說明:

![]() 相關商品:

HDL Works IO Checker v2.2.R3 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v3.0 R3 for Linux x64 英文正式版(電路檢查軟體)

HDL Works IO Checker v2.3 R1 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v2.1 R2 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v2.2 R4 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v2.1 R4 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v3.2.R1 for Linux x64 英文正式版(HDL代碼優化軟體)

相關商品:

HDL Works IO Checker v2.2.R3 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v3.0 R3 for Linux x64 英文正式版(電路檢查軟體)

HDL Works IO Checker v2.3 R1 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v2.1 R2 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v2.2 R4 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v2.1 R4 for Linux 英文正式版(電子設計軟體)

HDL Works IO Checker v3.2.R1 for Linux x64 英文正式版(HDL代碼優化軟體)